Le nuove famiglie di microcontrollori a 32 bit a90nm di Freescale Semiconductor sono costruite utilizzando il core ColdFire V1 e il core ARM Cortex-M4. Ogni core possiede delle caratteristiche che lo rendono la scelta appropriata per molti spazi d'applicazione embedded.

Core ColdFire Versione 1

Progettato per applicazioni entry-level a 32 bit, l'obiettivo principale del core ColdFire V1 consiste nella minore dispersione possibile di energia. Versione semplificata delle core ColdFire V2, la V1 presenta una gestione migliore degli operandi a 8 bit e a 16 bit, mentre mantiene le stesse modalità di indirizzamento e le stesse definizioni di istruzione dell'architettura ColdFire.

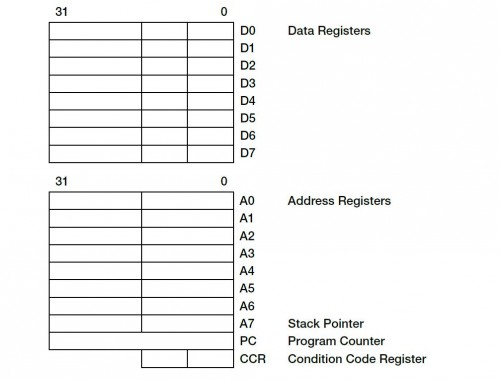

La figura mostra il modello di programmazione dell'utente, che include:

-

- 16 registri a 32 bit general-purpose (8 registri di dati, D[0-7] e 8 di indirizzi, A [0-7])

- Pc a 32 bit

- Registro dei Code a 8 bit (CCR, condition code register)

L’ISA definisce le operazioni di lunghezza variabile dove le istruzioni possono essere a 16, 32 o 48 bit in lunghezza e includere un potente set di modalità di indirizzamento della memoria dei dati. Operando i dati supportati sono gli interi a 1, 8, 16 e 32 bit. In aggiunta alle operazioni di caricamento e immagazzinamento della memoria, l’ ISA supporta le istruzioni di carico e i movimenti memory – to – memory. L'unità EMAC (enhanced multiply-accumulate) inclusa nelle famiglie MCF51Qx/Jx aggiunge il supporto per le istruzioni composte MAC + Move, l’indirizzamento alla coda di memoria circolare e quattro registri di accumulatore a 48 bit.

Il nucleo dell'architettura include il supporto per le istruzioni di un coprocessore generico e una interfaccia hardware per accelerare le operazioni al livello di una istruzione o di una funzione. Un esempio è rappresentato dalla CAU (cryptographic acceleration unity, unità di accelerazione crittografica). Il CAU offre un notevole incremento delle prestazioni a un certo numero di algoritmi di sicurezza molto popolari al momento, inclusi DES, AES, SHA1, SHA-256 e MD5 ad un piccolo costo di hardware. L'interfaccia del coprocessore per mettere un acceleratore accoppiato saldamente dove la CPU va a prendere gli operandi e invia i comandi agli moduli hardware.

Come tutte le implementazioni del processore ColdFire, il core ColdFire V1 usa un IFP (Instuction Fetch Pipeline) a due stadi e un OEP (Operand Execution Pipeline) a due stadi per offrire un'appropriata implementazione hardware in modo da gestire il set di istruzioni a lunghezza variabile. Il core si interfaccia al SoC per mezzo di un singolo bus a 32 bit AMBA AHB. Le interfacce di memoria IFP e OEP vengono messe insieme e mappate direttamente nel bus pipelined AHB a due stadi (fase di indirizzamento e fase di dati).

Sono sempre molto interessato ai progetti volti al risparmio energetico… Speriamo che altri progetti portino qualcosa di concreto nelle vendite commerciali dei sistemi hardware. (In fondo qualcosa si sta muovendo ma è davvero poco)

Al dì là della presentazione sarebbe necessaria un applicazione pratica del dispositivo almeno per avvicinare quelli che sono interessati all’utilizzo.