Il dispositivo Virtex di Xilinx è un dispositivo logico programmabile i cui blocchi sono caratterizzati mediante un file di estensione .BIT. I dispositivi Virtex™ sono configurabili caricando dati (configuration data) nella sua memoria interna. Alcuni dei pins del package sono utilizzati per l’operazione di set-up (sono quindi pins dedicati), mentre altri sono disponibili per altri usi, come I/O, sempre che siano stati precedentemente configurati. In questo articolo verrà illustrata la struttura di questo file con particolare riferimento alla sezione iniziale detta header.

INTRODUZIONE

Il dispositivo Virtex™, user-programmable gate array, contiene una serie di elementi configurabili. I due elementi più importanti sono identificati come:

- CLBs, Configurable Logic Blocks, fornisce gli elementi funzionali per la costruzione della logica interna.

- IOBs, Input/Output blocks, fornisce l’interfaccia tra il package pins e i CLBs.

Oltre a questi importanti blocchi esistono altri che sovrintendono ad altre funzionalità:

esiste il BRAMs, blocchi di memoria ognuno costituto da 4096 bits, il clock DLL, per la distribuzione del clock. Il .bit file è costituito da diverse parti, la sezione iniziale è denominata header, questo contiene informazioni sul file stesso, seguito da bitmap data o raw bit stream che iniziano con il valore esadecimale 0xFFFFFFFF 0xAA995566 (synchronize word).

VIRTEX™, UNA FAMIGLIA DI FPGA

I componenti Virtex™ identificano una famiglia di FPGA della casa costruttrice Xilinx, e comprende componenti quali per esempio Virtex-5, Virtex-4, Virtex-II Pro, Virtex-II e Virtex-E. Questi sono utilizzati in una varietà di applicazioni da telecomunicazioni a utilizzi video, medicali, networking, e così via. BitGen è un tool utilizzato per produrre dei bitsream per configurare i dispositivi. Infatti, al termine del progetto è necessario configurare il dispositivo per fare in modo che questo esegua la data funzionalità. In questo processo viene utilizzato il tool BitGen che, a fronte di un NCD (Native Circuit Description) produce un bitstream configuration file: questo è un file binario con l’estensione .bit. I dati contenuti nel .bit file sono caricati nell’FPGA o utilizzati per ricavare un PROM file. BitGen n non produce solo il “.bit” file, infatti a seconda delle opzioni utilizzate mediante il comando bitgen [options] infile[.ncd] [outfile] [pcf_file.pcf], possono essere generati diversi tipi di file, per esempio:

- .rbt - (prodotto quando viene specificato l’opzione “-b”) – È una versione ASCII del “.bit” file.

- .bit - (viene prodotto con l’opzione “-j”) – Questo è un file binario che contiene “proprietary header information” come dati di configurazione. Questo è utilizzato come input verso altri Xilinx tool come PROMGen e iMPACT.

- .bgn - (sempre prodotto) – Contiene informazioni che tecnicamente chiameremo “log information” per BitGen come opzioni della linea di comando, errori e warnings.

- .drc - (viene sempre generato a meno che non si indica l’opzione “-d”) – Contiene log information o Design Rules Checker, incluso anche errori e warnings.

- .isc – contiene i dati di configurazione nel formatoIEEE-1352 quando “-g IEEE:1532:Yes” viene specificata.

- .bin - (Podotto quando viene specicato “-g Binary:Yes”) questo è un file binario che contiene solo i dati di configurazione (questo non ha una sezione header come il “.bit” file).

HEADER

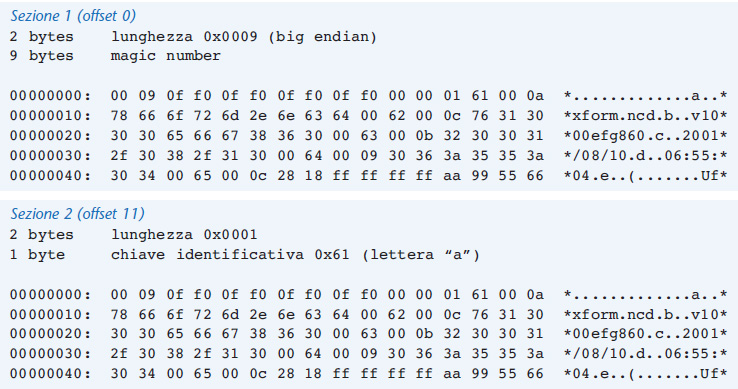

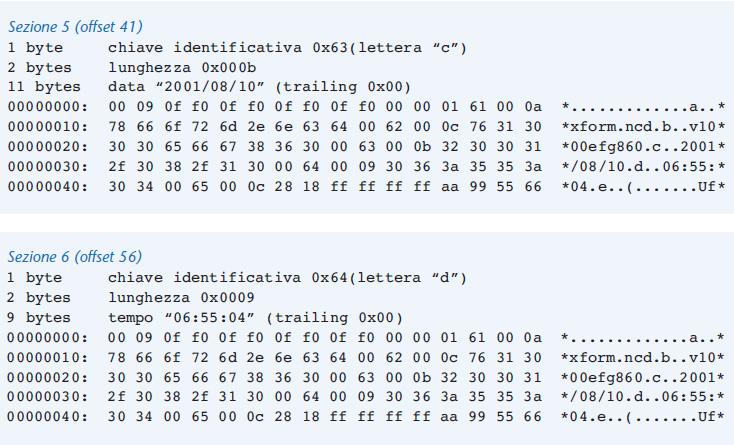

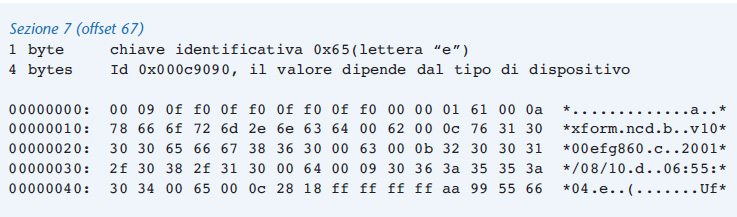

La struttura del file che è mostrata nelle figure 1-4, ed è stata ottenuta con un’operazione di dump di un “.bit” file (figura 1 e 2).

Le informazioni all’interno dell’header sono divise in sette sezioni: Sezione 1 (offset 0): è costituito da due campi di cui il primo identifica la lunghezza (2 bytes) espresso in big endian del magic number del formato del file. Sezione 2 (offset 11): è costituita sempre da due campi: lunghezza (2 bytes) della sezione e il codice ascii della lettera ‘a’ (ASCII 0x61) e la chiave identificativa. Sezione 3 (offset 14): è sempre formata da due campi: lunghezza (2 bytes) della stringa e la stringa del design del progetto in ASCII e la stringa alfanumerica del progetto. Sezione 4 (offset 26): è formata da tre campi: uno identifica la lettera ‘b’ in ASCII (0x62), il secondo campo identifica la lunghezza del part name e a seguire viene riportato il nome stesso. Sezione 5 (offset 41): è sempre di tre campi e identifica la data ed è formata dai seguenti parametri: il carattere ASCII della lettera ‘c’, la lunghezza del campo e la data. Sezione 6 (offset 56): è formata sempre da tre campi: il carattere ASCII della lettera ‘d’, la lunghezza del campo e il tempo. Sezione 7 (offset 67): è sempre di tre campi: il carattere ASCII della lettera ‘e’, la lunghezza del campo e il codice alfanumerico che individua il dispositivo fisico utilizzato. Dopo l’header seguono dei bitmap data (figura 3 e 4).

Quando si parla di dati da caricare su una FPGA si parla di bitstream. Ovvero la connettività e l’instradamento delle risorse logiche sulla FPGA. Il flusso di dati si basa su diversi formati, alcuni specifici del produttore registrati come sequenze di macro.