I chip della Analog Devices serie ADuC7000 rappresentano un’ottima scelta per lo sviluppo di sistemi embedded mixed-signal. Dotati di un core ARM7®TDMI 32-bit RISC sono in grado di raggiungere velocità di campionamento fino a 1MSPS. La famiglia dei Microconverter della Analog Devices unisce al microcontrollore ed alla flash embedded, periferiche analogiche di elevata precisione, come i 12 ADC, i DAC, un riferimento di tensione a bandgap ed un sensore di temperatura. Essi si suddividono in due principali categorie, di cui una per applicazioni di basso e medio livello, l’altra destinata ad applicazioni professionali in cui si richiede maggiore velocità e di memoria.

Introduzione

La serie ADuC7000 e il core ARM7®TDMI

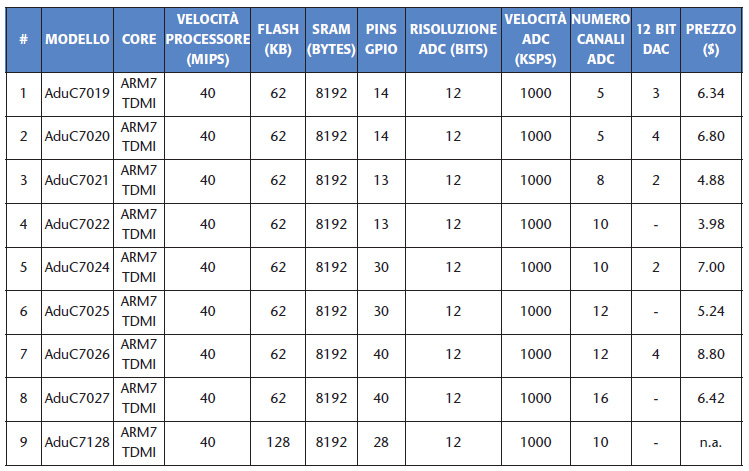

La prima delle due categorie è basata su core 8051 ed è indicata con la sigla ADuC8xx [1], mentre la seconda, dotata di un core ARM7®TDMI 32-bit RISC, è conosciuta come serie ADuC7000. La Tabella 1 riassume le caratteristiche più importanti di tutti i modelli di quest’ultima famiglia.

Il core ARM7 [2] utilizza un singolo bus a 32-bit per dati e programma. La lunghezza dei dati può essere 8, 16 o 32bit, mentre quella di una instruction word deve essere necessariamente a 32bit. L’architettura ARM7®TDMI implementata sulla serie ADuC7000 è un versione modificata rispetto al classico core ARM7. Essa presenta, in particolare, quattro caratteristiche addizionali:

- T: Supporto per un set di istruzioni a 16bit (Thumb); questa caratteristica consente di utilizzare istruzioni a 16bit, disponendo quindi di una maggiore densità di codice e velocità di esecuzione delle operazioni.

- D: Supporto per il Debug;

- M: Supporto per le Moltiplicazioni tra long; sono state introdotte 4 operazioni extra che consentono di eseguire moltiplicazioni 32bit per 32bit, con il risultato memorizzato in un registro a 64bit; è possibile anche effettuare delle operazioni di tipo MAC (Multiply and ACcumulate).

- I: Include il modulo embeddedICE (In-Circuit Emulation) per il supporto del debugging embedded; esistono dei registri per breakpoint e watchpoint controllabili mediante interfaccia JTAG.

L’architettura ARM7 supporta 5 tipi di eccezioni:

- Interrupt normale (IRQ): è una sorgente di interruzione a priorità bassa; possono essere sia interni che esterni.

- Fast Interrupt (FIQ): è utilizzato per gestire trasferimenti di dati o canali di comunicazione a bassa latenza. Ovviamente un FIQ hanno la possibilità di interrompere un IRQ.

- Memory abort.

- Tentativo di esecuzione di una istruzione non

- Istruzione di interruzione software (SWI): può servire per effettuare un chiamata a sistema operativo.

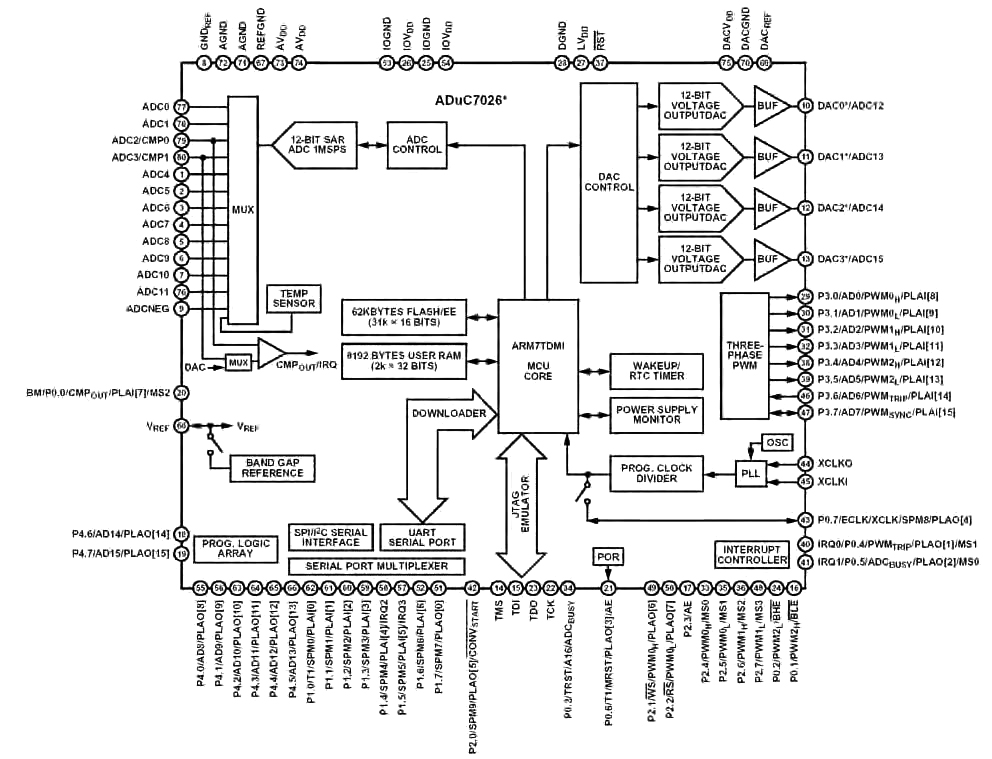

Il core ARM7 dispone in totale di 37 registri di cui 31 general-purpouse e 6 di stato. La Figura 1 riporta lo schema a blocchi un tipico processore della seria ADuC7000 ed il relativo pinout.

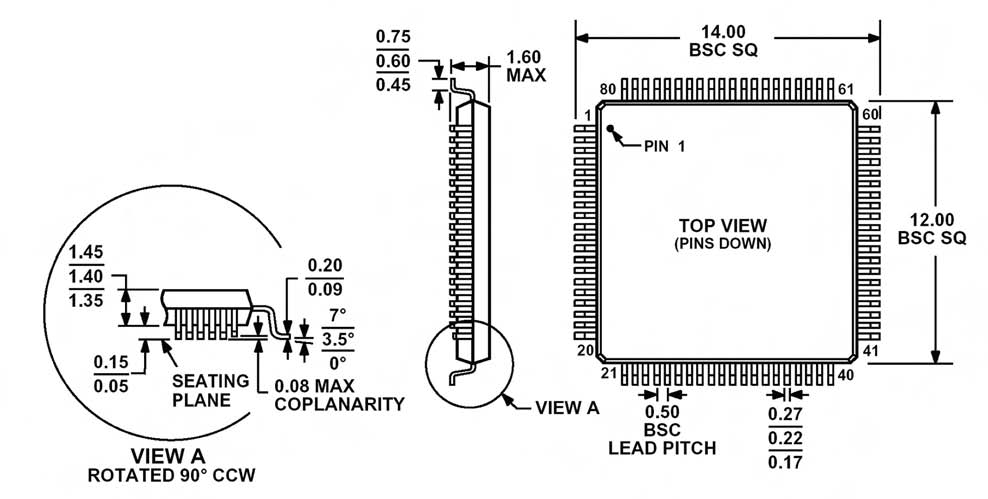

Mentre in Figura 2 è riportata un dettaglio del package e le relative dimensioni.

Come si nota l’area occupata (appena 168mm2) è davvero ridotta, grazie anche all’uso di un contenitore di tipo LQFP. Dopo una breve e doverosa presentazione di questi chip, si passerà ad analizzare in dettaglio le loro caratteristiche di punta: le periferiche analogiche. Ci si soffermerà soprattutto sui convertitori analogico/digitale (ADC), con uno sguardo anche ai DAC ed al comparatore. Infine, sarà presentato un esempio di programmazione in C in cui si effettua la conversione digitale di un segnale, inviato successivamente alla porta seriale.

LA SEZIONE ANALOGICO/DIGITALE (ADC)

Caratteristiche

Il convertitore analogico/digitale incorpora un ADC SAR multicanale ad alta velocità. Esso può operare con tensioni da 2.7V a 3.6V. La velocità massima di conversione è pari a 1MSPS (Milioni di campioni al secondo) se la sorgente di clock è 41.78MHz. L’intero blocco, oltre che dall’ADC, è costituito da un multiplexer, da un T/H differenziale e un riferimento di tensione interno. Il converter è basato sulla tecnica SAR (ad approssimazioni successive) e utilizza due DAC per il percorso di retroazione. La risoluzione nominale è 12bit. Il convertitore è in grado di adattarsi al tipo di segnale proveniente dall’ingresso. Infatti, dispone di 3 modalità operative, impostabili via software tramite i registri interni. Tali modalità sono di seguito elencate e descritte:

- Modalità Differenziale, per segnali piccoli e bilanciati.

- Modalità single-ended, per segnali sbilanciati.

- Modalità pseudo-differenziale, per qualunque segnale sbilanciato in cui la reiezione del modo comune è un parametro critico.

Il convertitore accetta un segnale in ingresso compreso tra 0V e VREF quando opera nelle modalità 2 e In quella differenziale, il segnale di ingresso deve essere bilanciato intorno al modo comune (VCM), con una escursione massima pari a 2VREF (la figura 3 chiarisce il concetto). Oltre, al già citato riferimento interno (2.5V), è possibile utilizzarne uno esterno.

La conversione può essere avviata sia in modalità continua che singola. Come segnale di trigger per l’inizio della conversione può essere utilizzato il pin /CONVSTART, l’output generato dal PLA, l’overflow del Timer0 o del Timer1. Oltre ai segnali analogici, esiste un altro ingresso che può essere inviato al MUX: il sensore di temperatura interno. Esso può essere utilizzato per misurare la temperatura del die, con una precisione garantita di ±3°C.

Funzione di trasferimento

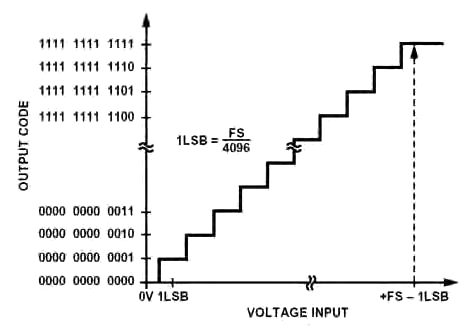

Nella modalità single-ended e pseudo-differenziale, il range di ingresso è 0V-VREF. La codifica è binaria senza segno. La minima risoluzione (1 LSB) è ottenuta nel modo seguente:

1 LSB = FS/212 = 2.5V/4096 = 0.61mV = 610µV

Il calcolo è valido nel caso in cui si decida di utilizzare il riferimento di tensione interno. La caratteristica di trasferimento ingresso/uscita ideale è riportata in figura 4.

Ovviamente, questa caratteristica è ideale poiché non tiene conto degli errori introdotti da un ADC (errore di linearità, di offset, di guadagno, differenziale, etc.). Nel caso differenziale il segnale è applicato ai pin VIN+ e VIN. La massima ampiezza del segnale differenziale è compresa tra –VREF e +VREF. (quindi 2VREF). La tensione di modo comune, (VIN+ + VIN)/2, deve essere impostata esternamente. La codifica di uscita è in complemento a 2. La minima risoluzione è data da:

1 LSB = 2VREF /4096= 2·2.5V/4096 = 1.22mV = =1220µV

Anche in questo caso il calcolo è stato eseguito considerando il riferimento a 2.5V. La caratteristica di trasferimento ingresso/uscita ideale è riportata in figura 5.

Condizioni di funzionamento

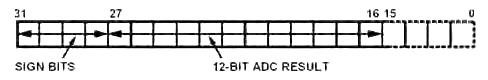

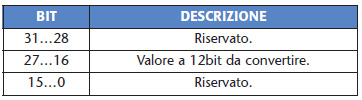

Il micro inserisce il risultato della conversione all’interno del registro ADCDAT, secondo il formato riportato in figura 6.

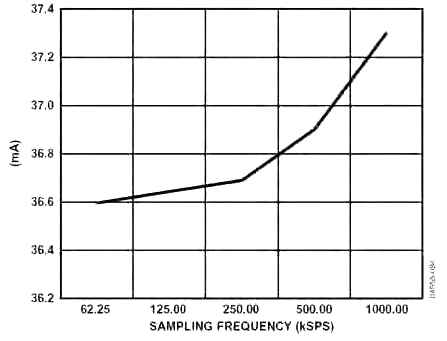

I primi quattro sono i bit del segno. Il risultato è inserito a partire dal bit 16 fino al bit 27. Il consumo di corrente, nella modalità standby (ossia ADC acceso ma non in esecuzione), è tipicamente 640µA. A tale valore bisogna aggiungere altri 140µA se si sceglie di utilizzare il riferimento interno. Infine, durante la conversione bisogna considerare altri 0.3µA · fSAMPLING(kHz). Il grafico del consumo di corrente dell’ADC in funzione della velocità di conversione è riportato in figura 7.

La figura 8 riporta l’andamento nel tempo dei diversi segnali che intervengono durante una conversione, quando è usato il segnale di trigger esterno.

Il pin ADCBUSY indica, se il suo valore logico è 1, che la conversione è in corso. Il registro ADCSTA permette invece di capire quando il risultato della conversione è disponibile per essere letto. Contemporaneamente, scatta l’interrupt dell’ADC.

Registri di configurazione

I registri che servono per configurare e controllare la sezione A/D sono 8. Essi sono di seguito elencati e descritti:

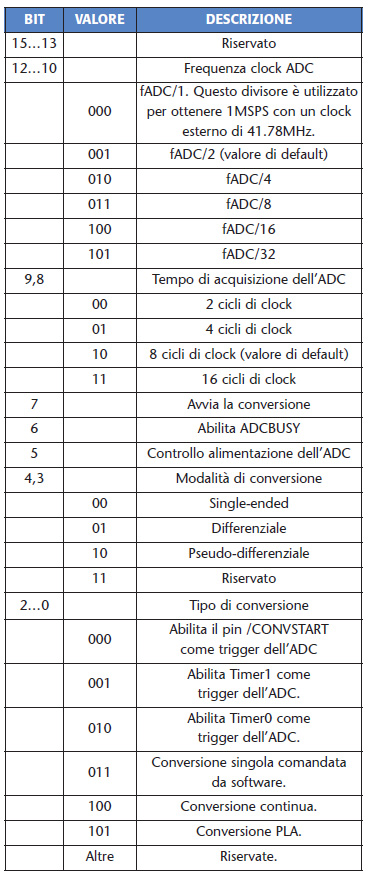

- ADCCON (tabella 2), è il registro che permette al programmatore di abilitare l’ADC, selezionare la modalità operativa ed il tipo di conversione.

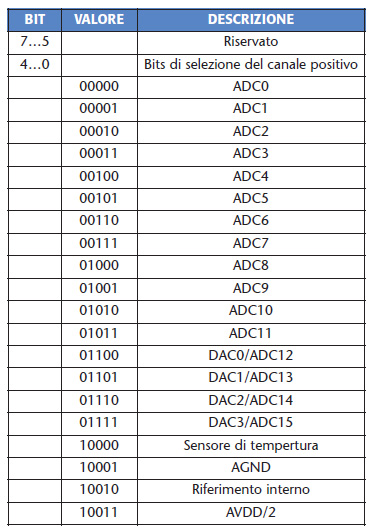

- ADCCP (tabella 3), permette di selezionare il canale positivo dell’ADC.

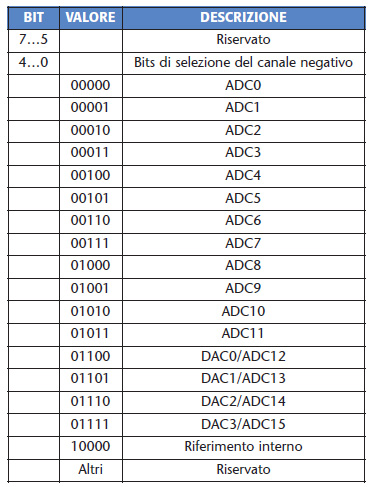

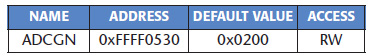

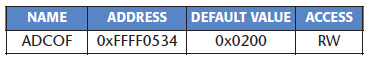

- ADCCN (tabella 4), permette di selezionare il canale negativo dell’ADC.

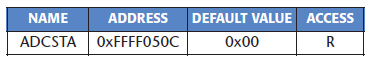

- ADCSTA (tabella 5), è il registro che indica quando il risultato di una conversione è pronto. Esso contiene solo un bit, ADCReady. Questo bit è portato ad 1 dal micro alla fine di ogni ciclo di conversione. Inoltre, esso ritorna a 0 automaticamente, quando viene letto il valore in ADCDAT. Quando è in esecuzione una conversione, lo stato dell’ADC può essere letto esternamente mediante il pin ADCBUSY (P0.5 delle linee general-purpose). Tale funzione deve, però, essere abilitata dal registro ADCCON.

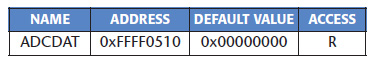

- ADCDAT (tabella 6), contiene il risultato della conversione, secondo lo schema di figura 6.

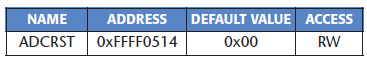

- ADCRST (tabella 7), scrivendo qualunque valore in questo registro si effettua il reset di tutti i registri relativi all’ADC, riportandoli al loro valore di default.

- ADCGN (tabella 8), serve per effettuare la calibrazione del guadagno

- ADCOF (tabella 9), serve per effettuare la calibrazione dell’offset.

Logica interna dell’ADC

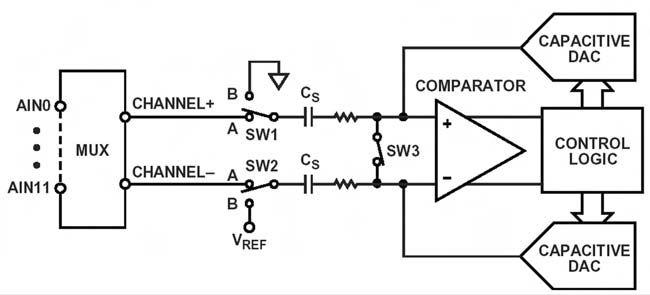

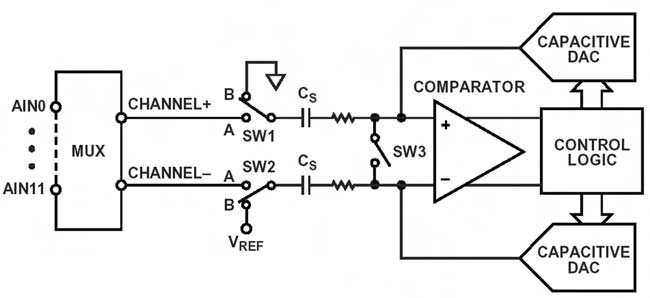

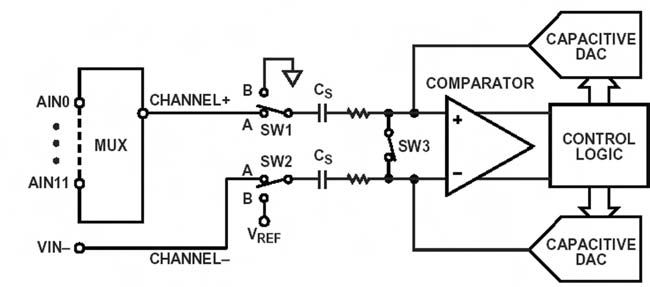

Il sistema di conversione è dotato, come già ricordato, di una architettura ad approssimazioni successive (SAR), con uno stadio a campionamento di carica nel percorso di retroazione. Questa struttura può operare in tre differenti modi: differenziale, pseudo-differenziale e single-eneded. Nella figura 9 è mostrato lo schema semplificato della fase di acquisizione per una configurazione differenziale.

L’interruttore SW3 è chiuso, mentre SW1 e SW2 sono in posizione A. Il comparatore è tenuto in uno stato bilanciato ed il valore del campione da convertire viene acquisito. La figura 10 mostra invece lo schema durante la fase di conversione.

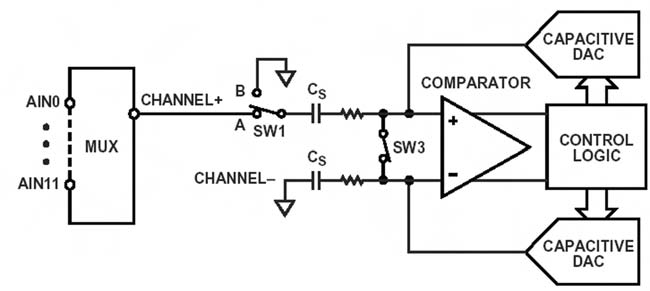

L’interruttore SW3 è aperto, mentre SW1 e SW2 sono portati in posizione B. In tale stato gli ingressi del comparatore diventano sbilanciati. Il codice di uscita è pronto quando i due DAC riportano gli ingressi del comparatore in uno stato bilanciato. Nella configurazione differenziale è importate che le impedenze delle sorgenti dei due ingressi (VIN+ e VIN) siano tra loro uguali, altrimenti il differente tempo di assestamento può comportare errori di conversione. Nella modalità pseudo-differenziale, si utilizzano sempre i pin VIN+ e VIN- come nella configurazione differenziale; lo switch SW2, però, può commutare su Channel- oppure su VREF. Il segnale di ingresso su VIN+ può variare tra VIN- e (VREF + VIN). Il segnale su VINREF + VIN-) non ecceda AVDD. La figura 11 chiarisce quanto sopra esposto.

Infine, nella configurazione single-ended, SW2 è connesso internamente a massa (figura 12).

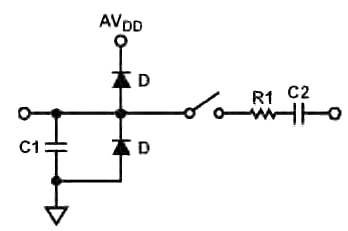

Il pin VIN- può essere lasciato floating. Il segnale di ingresso su VIN+ deve avere una dinamica compresa tra 0V e VREF. Circuito equivalente di ingresso La figura 13 riporta lo schema del circuito equivalente di ingresso dell’ADC.

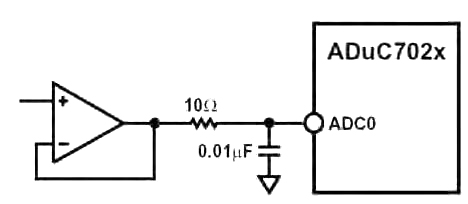

È importante tenere conto di tale schema per prevedere ed eventualmente eliminare effetti indesiderati. I due diodi garantiscono una protezione da scariche elettrostatiche (ESD), entrando in conduzione se il segnale di ingresso in modulo supera di 0.6V l’alimentazione. È importante sottolineare che una tale condizione è non distruttiva solo se la corrente nei diodi non supera i 10mA. Il condensatore C1 ha valore pari a 4pF ed è dovuto alla capacita esibita dal pin di ingresso. Il resistore R1, il cui valore è di 100o, è imputabile alla resistenza in conduzione dello switch elettronico. Infine, il condensatore C2 è quello necessario per il campionamento (16pF). Per applicazione in AC è consigliabile rimuovere le componenti ad alta frequenza dal segnale analogico, attraverso un filtro RC di tipo passa-basso. Inoltre, in tutte le applicazioni in cui il THD (Total Harmonic Distortion) e il SNR (Signal-to-Noise Ratio) sono parametri critici, l’impedenza di uscita della sorgente deve essere bassa. Se ciò non è vero allora bisogna utilizzare un buffer per ottenere una impedenza di ingresso teoricamente infinita (figura 14).

Riferimento di tensione bandgap

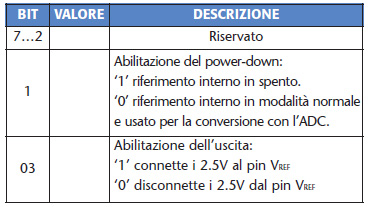

I microcontrollori della serie 7000 sono dotati di un riferimento di tensione a 2.5V che può essere usato sia per l’ADC che per il DAC. Inoltre, tale valore è reso disponibile sul pin VREF. Quando si decide di utilizzare il riferimento interno per la conversione, allora è necessario inserire un condensatore da 0.47mF tra il pin VREF e massa. Se invece si vuole sfruttare il riferimento di tensione per usi esterni, allora bisogna interporre un buffer poiché questo pin ha una ridotta corrente di uscita. Il riferimento può essere comandato da software (acceso e spento), tramite il registro REFCON (vedere tabella 10).

Esempio di programmazione

Il codice riportato nel listato 1 è un esempio di come effettuare la configurazione dell’ADC.

#include <ADuC7026.h>

void senddata(short);

void ADCpoweron(int);

char hex2ascii(char);

int main (void) {

//Configurazione ADC

ADCpoweron(20000); // Accensione ADC

ADCCP = 0x00; // Selezione del canale 0

REFCON = 0x01; // Connessione riferimento interno al pin Vref

GP0CON = 0x10100000; // Abilitazione uscita ECL su P0.7 e ADCbusy su P0.5

// Configurazione pin di TX e RX su P1.0 e P1.1

GP1CON = 0x011;

// Impostazione UART

COMCON0 = 0x80;

COMDIV0 = 0x88;

COMDIV1 = 0x00;

COMCON0 = 0x07;

//Conversione ed invio ad UART

while(1){

ADCCON = 0x7E3; // ADC config: fADC/2, acq. time = 16 clocks => ADC Speed = 1MSPS

while (!ADCSTA){} // Aspetta fine conversione

senddata (ADCDAT >> 16);

GP4DAT ^= 0x00040000; // Complementa P4.2

}

}

void senddata(short to_send){

while(!(0x020==(COMSTA0 & 0x020))){}

COMTX = 0x0A; // output LF

while(!(0x020==(COMSTA0 & 0x020))){}

COMTX = 0x0D; // output CR

while(!(0x020==(COMSTA0 & 0x020))){}

COMTX = hex2ascii ((to_send >> 8) & 0x0F);

while(!(0x020==(COMSTA0 & 0x020))){}

COMTX = hex2ascii ((to_send >> 4) & 0x0F);

while(!(0x020==(COMSTA0 & 0x020))){}

COMTX = hex2ascii (to_send & 0x0F);

}

char hex2ascii(char toconv){

if (toconv<0x0A){

toconv += 0x30;

}

else{

toconv += 0x37;

}

return (toconv);

}

void ADCpoweron(int time){

ADCCON = 0x20; // Accendi ADC

while (time >=0)

time--;

}

Listato 1

Lo stesso programma, dopo aver effettuato la conversione, inviata il valore digitale prelevato da ADCDAT ad una periferica collegata tramite interfaccia seriale (UART). Il listato 1 può essere considerato come un modello per iniziare a muovere i primi passi nella programmazione di questi micro. Anche se il codice si riferisce all’ADuC7026, esso è valido, con le dovute variazioni, anche per gli altri chip della stessa serie.

LA SEZIONE DIGITALE/ANALOGICO (DAC)

Caratteristiche

Gli ADuC7000 sono dotati, in base al modello, di 2, 3 o 4 convertitori digitali/analogici a 12bit (tabella 1). Ciascun DAC ha una tensione di uscita rail-to-rail capace di pilotare un carico 5kΩ/100pF. Il range della tensione di uscita può essere impostato secondo tre differenti opzioni:

- Da 0V a VREF.

- Da 0V a DACREF.

- Da 0V a AVDD.

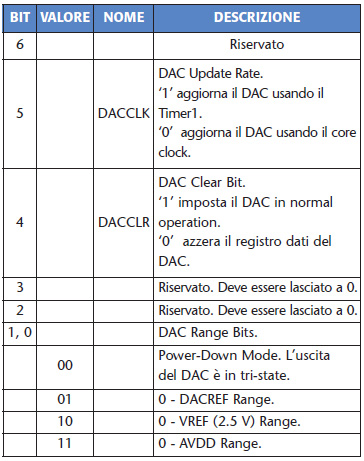

Ogni DAC è configurabile e controllabile indipendentemente mediante un registro di controllo (DACxCON) ed uno di dati (DACxDAT), secondo quanto riportato in Tabella 11 ed in Tabella 12.

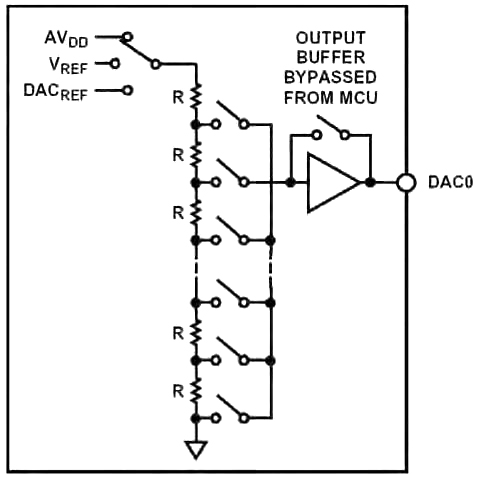

La struttura del DAC, come illustrato in figura 15, è costituita da una rete di resistenze, seguita da un buffer di uscita.

Quando si prende in esame un convertitore digitale/analogico è importante valutare la sua caratteristica di uscita. La bontà di un DAC è tanto maggiore quanto più lineare è tale funzione. Se si osserva la caratteristica dei DAC della serie 7000 (figura 16), si può osservare una degradazione della linearità solo in prossimità dei valori più bassi e più alti.

Tale comportamento è normale per un DAC, in quanto è dovuto alla saturazione dell’amplificatore di uscita. La caratteristica rappresentata in Figura 16 è riferita ad una dinamica tra 0V e AVDD (quella massima). Negli altri due casi, la situazione migliora verso l’alto poiché l’amplificatore non lavora ai limiti della sua alimentazione. Comunque, il comportamento rimane simile per i valori più bassi. Tutti i riferimenti riportati nel datasheet sono per un carico di 5kΩ. Se si vuole pilotare un carico superiore, allora la degradazione di linearità diventa maggiore, limitando significativamente la dinamica di uscita.

IL COMPARATORE

Caratteristiche

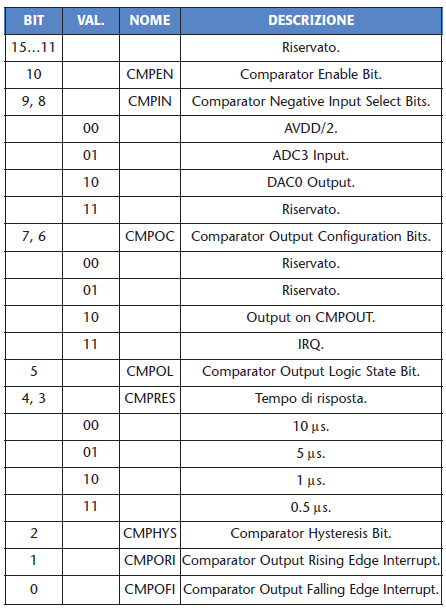

Tutti gli ADuC7000 integrano un compara- tore di tensione. L’ingresso positivo è multiplexato con il pin ADC2, mentre per quello negativo ci sono due opzioni: ADC3 oppure DAC0. Il comparatore è molto versatile in quanto è possibile configurare la sua uscita per generare un interrupt, portarlo direttamente all’esterno, usarlo per avviare una conversione o ancora portarlo alla logica programmabile (PLA). Esso è controllato mediante il registro CMPCON (Tabella 13), tramite il quale si può decidere l’offset di ingresso e l’isteresi come nel classico trigger di Schmitt.

Riferimenti bibliografici:

[1] Sito Analog Device, www.analog.com

[2] “ARM Architecture Reference Manual”

www.altera.com/literature/

third-party/ddi0100e_arm_arm.pdf

I chip ADuC7000 implementano, come fanno ancora oggi molti micro, convertitori ADC ad approssimazioni successive. Gli ADC SAR trovano largo impiego in varie applicazioni di controllo e acquisizione dati grazie all’alta risoluzione che riescono a raggiungere, combinando nello stesso tempo un basso consumo energetico.

Buongiorno

Volevo chiedere senza fare pubblicità a nessuno, se qualche lettore può darmi un idea riguardo a qualche starter kit è sw. relativi , per cominciare in maniera facile a valutare un ADuC7000 oppure un altro Micro della famiglia.

Grazie ed i miei modesti complimenti per l’articolo molto interessante.

Attilio

Puoi vedere QuickStart Plus for ADUC702X. Sul sito Analog Device trovi delle info.